这台机器可以让摩尔定律保持在正规上

ASML的高数值孔径极紫外光刻机EXE:5000的照片说明了它的巨大规模。来源:ASML

在过去的半个世纪里,我们已经开始把摩尔定律——硅领域中晶体管数量大约每两年翻一番,推动计算向前发展的增益——看作是刚刚发生的事情,就好像它是一个自然的、不可避免的过程,类似于进化或衰老。当然,现实情况大不相同。与摩尔定律保持同步需要花费几乎难以想象的时间、精力和人类智慧——成千上万的人生活在多个大陆,数不清的土地上摆放着地球上最复杂的机器。

也许这些机器中最重要的就是进行极紫外线(EUV)光刻。EUV光刻技术是几十年研发的成果,如今已成为过去两代尖端芯片的驱动技术,在过去三年中,EUV光刻技术用于所有高端智能手机、平板电脑、笔记本电脑和服务器。 然而,摩尔定律必须继续前进,芯片制造商继续推进他们的路线图,这意味着他们将需要进一步缩小器件的几何尺寸。

所以,在ASML,我和我的同事们正在开发下一代光刻技术。 它被称为高数值孔径EUV光刻技术,需要对系统的内部光学系统进行重大检修。 高数值孔径EUV光刻技术预计在2025年投入商业使用,芯片制造商将依靠其在本十年末实现承诺的进步。

01

光刻的三个因素

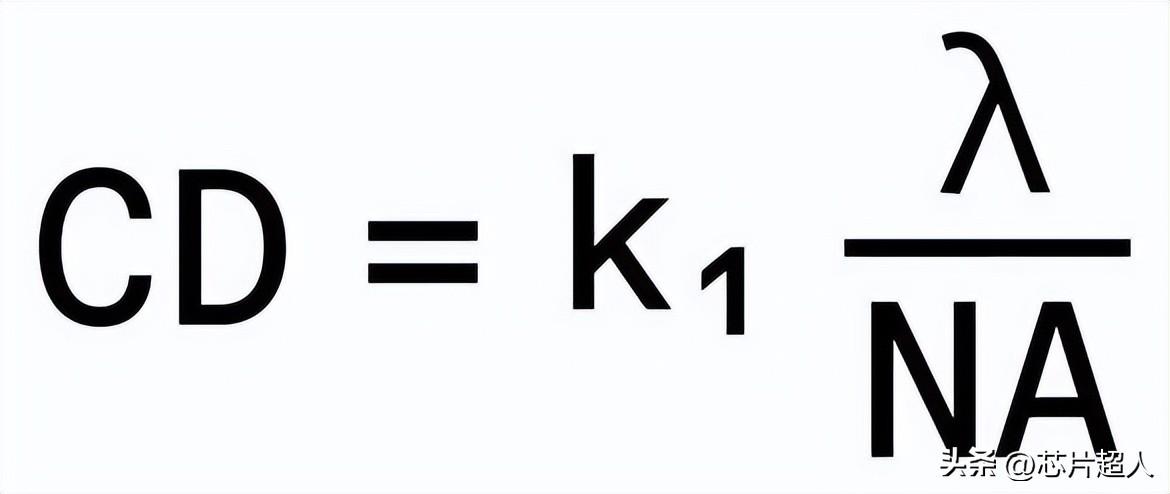

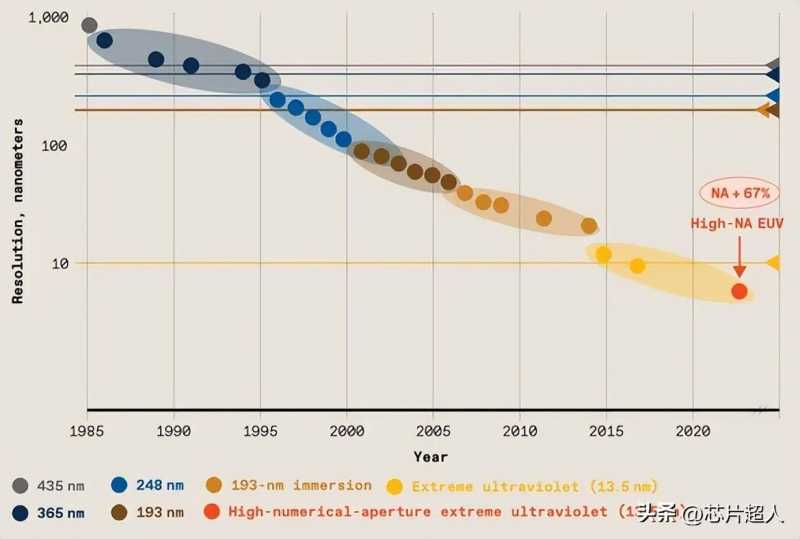

摩尔定律依赖于提高光刻技术的分辨率,以便芯片制造商能够铺设更精细的电路。在过去的35年中,工程师们通过研究三个因素的组合,实现了两个数量级的分辨率降低:光的波长、k1(封装过程相关因素的系数)和数值孔径(NA)(衡量系统发光角度范围的指标)。

临界尺寸——即你可以用某种光刻曝光工具打印的最小特征尺寸——与光波长除以光学器件的数值孔径成正比。 所以,你可以通过使用更短的光波长或者更大的数值孔径,或者两者组合来获得更小的临界尺寸。例如,可以通过改进生产过程控制,使k1值尽可能接近 0.25 的物理下限。

一般来说,提高分辨率的最经济的方法是增加数值孔径、改进工具和过程控制,以实现更小的k1值。 只有当芯片制造商没有进一步改善数值孔径和k1值的选择后,他们才求助于降低光源的波长。

然而,该行业不得不多次改变波长。20世纪90年代末,波长由汞灯产生的365纳米通过氟化氪激光器发展到248纳米,在本世纪初又通过氟化氩激光器发展到193纳米。 在工业跃升到更短的波长之前,每一代光刻系统的数值孔径逐渐增大。

例如,随着193纳米技术的应用接近尾声,一种新的增加数值孔径的方法被引入:浸没式光刻。通过在透镜底部和晶圆之间放置水,NA可以从0.93显着扩大到1.35。自 2006 年左右推出以来,193 纳米浸没式光刻技术就成为业界最前沿光刻技术的研究热点。

在过去的四十年中,光刻技术的分辨率提高了大约一万倍。 这部分是由于使用了更小的光波长,但也需要更大的数值孔径和改进的处理技术。(来源:ASML)

02

EUV的黎明

但是,随着制造小于 30 纳米特征的需求增加,以及 193 纳米光刻技术的 NA 已达到极限,跟上摩尔定律的步伐变得越来越困难。

要制造小于30纳米的特征,要么使用多个图案来制作单层芯片特征——这在技术和经济上都是一项繁重的技术,要么就需要改变波长。经过 20 多年前所未有的开发努力,下一个新波长才得以问世:13.5 纳米EUV。

EUV需要一种全新的发光方式。 这是一个非常复杂的过程,需要用强大的二氧化碳激光在飞行途中撞击熔化的锡金属液滴。激光将锡蒸发成等离子体,发出光子能量的光谱。从这个光谱中,EUV光学系统收集所需的13.5纳米波长,然后通过一系列反射镜将其反射到图案掩模上,将图案投射到晶圆上。 所有这些都必须在超净真空下进行,因为13.5纳米波长会被空气吸收。 (在前几代光刻技术中,光通过掩模投射到晶圆上。 但是EUV很容易被吸收,因此掩模和其他光学元件必须具有反射性。)

长方形机器的剖面图。 紫色光束从机器内的物体上反射。在真空室中,EUV光(紫色)在从光掩模(顶部中心)反射之前,被多个镜面反射。 从那里,光继续它的旅程,直到它被投射到晶圆片(底部中心)上,带着光掩模的图案。 图示显示当今的商业系统,数值孔径为0.33。 未来系统中的光学系统将有所不同,数值孔径为0.55。(资料来源: ASML)

从193纳米光转换到EUV,在一定程度上降低了临界尺寸。 为了利用光刻技术的局限性,被称为“制造用设计”的过程,包括设置电路块的设计规则,在降低k1值方面做了很多工作。从现在的0.33到0.55, 现在是时候再次提高数值孔径了。

03

让高数值孔径EUV

发挥作用

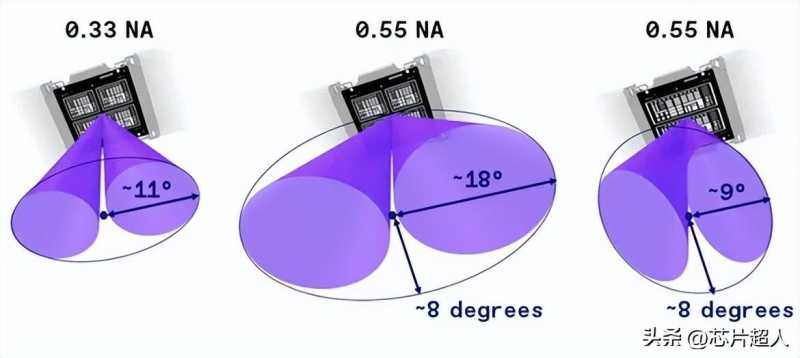

将数值孔径从今天的0.33提高到目标值0.55不可避免地需要一系列其他调整。 像EUV光刻这样的投影系统,在晶圆片上和掩模上都有数值孔径。当你在晶片上增加数值孔径时,它也会增加掩模上的NA。因此,在掩模处,入射光锥和出射光锥变大,必须相互倾斜以避免重叠。 重叠的光锥会产生不对称的衍射图案,从而产生令人不悦的成像效果。

但是这个角度是有限的。 由于EUV光刻所需的反射掩模实际上是由多层材料制成的,因此无法确保在特定反射角以上获得适当的反射。EUV掩模的最大反射角为11度。还有其他的挑战,但反射角是最大的挑战。

曲线图向上弯曲,然后向右下降。下降的一个点被突出显示。如果EUV光以过于陡峭的角度照射掩膜,就无法正常反射。(来源:ASML)

一排三幅图像显示紫色圆锥体指向一个图案化的正方形。在今天的EUV中,掩模的反射角处于极限(左),增加EUV数值孔径将导致反射角过宽(中)。 因此,高数值孔径EUV使用非晶态光学,只允许角度在一个方向上增加(右)。 这样可以成像的场的大小是掩模的一半,因此掩模上的图案必须向一个方向变形,但这足以维持通过机器的吞吐量。(资料来源: ASML)

克服这一挑战的唯一途径是提高一种被称为“消磁”的质量。 消磁就像它听起来的那样——从面具上取下反射的图案并缩小它。为了弥补反射角的问题,我和我的同事不得不将退焦倍率提高一倍,达到8倍。 因此,在晶圆片上成像的掩模部分会小得多。 较小的图像场意味着它需要更长的时间来生成完整的芯片图案。 事实上,这一要求将使我们高数值孔径扫描仪的吞吐量降低到每小时100片以下——这一生产率水平将使芯片制造变得不经济。

值得庆幸的是,我们发现只需要增加一个方向的退磁,即反射角最大的方向。其他方向的退磁可以保持不变。这样,晶圆上的磁场尺寸就可以接受了——大约是当今 EUV 系统所用尺寸的一半,即 26 x 16.5 毫米,而不是 26 x 33 毫米。这种与方向有关的消磁(或称变形消磁)构成了我们的高 NA 系统的基础。光学元件制造商卡尔蔡司(Carl Zeiss)为设计和制造符合我们新机器所需规格的变形透镜付出了巨大的努力。

为了确保与半尺寸场相同的生产率水平,我们必须重新设计系统的光圈和晶圆台(分别容纳掩模和晶圆台的平台),并在扫描过程中使它们彼此同步。 这种重新设计的结果是纳米级精度,加速地提高了四倍。

04

2025年

高数值孔径EUV产量情况

第一个高数值孔径EUV系统,ASML EXE:5000,将于2024年初安装在我们与比利时纳米电子研究机构Imec联合开设的新实验室中。 该实验室将允许客户、掩模制造商、光刻胶供应商和其他人开发实现高数值孔径EUV所需的基础设施。

我们必须实现这一目标,因为高数值孔径EUV是维持摩尔定律的重要组成部分。 不过,达到0.55 NA 并不是最后一步。 从那时起,ASML、蔡司和整个半导体生态系统将进一步向更好、更快、更具创新性的技术迈进。

来源:内容由芯世相(ID:xinpianlaosiji)编译自「IEEE Spectrum」,作者:Jan van Schoot

大家都在看

-

中外交流丨镜头下的沙海新绿——从图片展上的照片看新疆带给世界的治沙灵感 “大美新疆铸辉煌——纪念新疆维吾尔自治区成立70周年”主题图片展12月10日在哈萨克斯坦国家博物馆拉开帷幕。哈国家博物馆馆长阿布德哈利乌勒致辞说,本次图片展在哈萨克斯坦成功开幕,是两国人民民心相亲、精神与智 ... 机械之最12-17

-

中国玩具如何“玩转”全球大市场? 原标题:科技范儿、文化范儿、绿色范儿——中国玩具“玩转”全球大市场在义乌全球数贸中心,外国客商与经营户洽谈采购事宜。王怿杰摄在义乌全球数贸中心,商家展示可变形智能玩具。王怿杰摄广东新佳奇科技有限公司工 ... 机械之最12-17

-

专科生逆袭!2026机械专业必考8大黄金证书,好就业薪资高! 各位机械专业的大专同学们,是否在思考如何提升竞争力,获得高薪工作?答案就在考取高含金量证书。在智能制造时代,“技能+证书”是你最硬的敲门砖。2026年大专机械设计与制造专业最值得投资的8大证书,能直接助力你 ... 机械之最12-17

-

在寒风中飘落的树叶是麻烦还是资源?每年520万吨枯枝落叶去哪了 深秋初冬,落叶玩家“卷”了起来:他们收集好看的叶子,亲手做成一顶魔法帽、一件披风或是扎成一把花束,用自己的巧思延长落叶的生命。京城的树郁郁葱葱。统计显示,每年的枯枝和落叶达到了惊人的520万吨,而且仍在 ... 机械之最12-17

-

跃升48位!太重再次荣登“中国机械500强”榜单 近日,2025年中国机械500强研究报告发布会暨中机企协业务总部启用仪式圆满落幕。太重凭借优异表现和雄厚实力,再次荣登“2025中国机械500强”与“2025中国机械500大”双榜单,其中“2025中国机械500强”较去年跃升48 ... 机械之最12-17

-

Anthropic重磅新研究:当AI采访了1250人,它看见了人类的“职业软肋” AI不仅能回答问题,还能采访人类了。Anthropic让模型与1250名真实用户深度对话,自动写提纲、追问、做聚类分析,最后画出一张「人类情绪雷达图」。这一次,人类成了AI的研究对象。很难想象,有一天AI真的开始采访人 ... 机械之最12-16

-

世界五大军事家第5名:成吉思汗 —— 冷兵器时代最恐怖的战争机器 图片来源于网络如果战争是一门关于破坏与征服的极端艺术,那么成吉思汗无疑是这门艺术史上最伟大的工程师。他并非仅仅是一位骑兵统帅,而是一位颠覆了草原规则、重塑了战争逻辑的帝国缔造者。他的蒙古军团,是中世纪 ... 机械之最12-16

-

“十四五”期间 太原市强化企业创新主体地位 激发创新活力 创新驱动发展,技术引领未来。在科技竞争日益激烈的背景下,作为市场主体的企业,创新能力已成为衡量企业乃至城市核心竞争力的关键指标。 “十四五”期间,我市强化企业创新主体地位,推进企业与国内大院大所 ... 机械之最12-16

-

理科专业解读一:从学业到就业,一文搞懂机械类专业! 机械类专业,由于其布点院校多、招生规模大、社会应用性强、就业前景广阔,成为无数考生与家庭青睐的务实选择。因此几乎每年都是高考志愿填报的“重头戏”。本期飞翔老师将带大家详细盘点和梳理机械大类下各专业的培 ... 机械之最12-15

-

大专生逆袭!2026机械设计与制造专业必考8大证书 各位机械专业的同学,你是否担心专科学历在求职时缺乏竞争力?是否觉得传统机械行业薪资天花板触手可及?在智能制造与工业4.0席卷全球的今天,仅凭一张毕业证早已不够。精准考取高含金量证书,是你打破学历局限、实 ... 机械之最12-15

相关文章

- 高考志愿填报常识34:中国机械“五虎四小龙”

- 在寒风中飘落的树叶是麻烦还是资源?每年520万吨枯枝落叶去哪了

- 跃升48位!太重再次荣登“中国机械500强”榜单

- Anthropic重磅新研究:当AI采访了1250人,它看见了人类的“职业软肋”

- 废墟上,他们把日子重新拧上弦

- 世界五大军事家第5名:成吉思汗 —— 冷兵器时代最恐怖的战争机器

- “十四五”期间 太原市强化企业创新主体地位 激发创新活力

- 外骨骼机器人“出圈” 行业痛点待解

- 理科专业解读一:从学业到就业,一文搞懂机械类专业!

- 大专生逆袭!2026机械设计与制造专业必考8大证书

- 一级军士长的带兵“三字诀”

- 卖“陪伴”成了生意经?为什么大家都不想独处了

- 四大维度,深度解析2025年中国机械工业500强

- 不要温和地走入AI时代:一封写给青少年的书信

- 太重再次荣登“中国机械500强”榜单

- 马钧:被正史忽略的三国机械之神一具水车救活万民,诸葛亮都叹服

- 《时代》周刊2025年度人物:AI缔造者

- 湖北十堰调查组通报“最忙五人组”事件

- 是必需品还是智商税?空气净化器,有些是不是“吹”过头了?

- AI与人文的“危”与“机”——读《AI时代的文学教育》

热门阅读

-

天下第一暗器暴雨梨花针,传说中的唐门暗器做出来了 07-13

-

世界十大大型船舶排名,第一能承重六十万吨! 07-13